The purpose of this handout is to explain how to use the internal 8051 timers to generate time delays.

Uses of Timers & Counters:

Uses of Timers & Counters:

- Interval Timing

- Periodic event timing

- Time base for measurements

- Event Counting

- Baud Rate Generation

- 2 timers (Timer 0 and Timer 1)

- 16-bit timers (65,535) max

- Flag is set when the timer overflows

- Timers can be based on internal clock (OSC/6) or from external source (counter mode).

Timer Registers:

- TCON Timer Control

- TMOD Timer Mode

- TH0/TL0 Timer 0 16 bit register (byte addressable only)

- TH1/TL1 Timer 1 16 bit register (byte addressable only)

Timer/Counters:

The Atmel 80C51 Microcontrollers implement two general purpose, 16-bit timers/counters. They are identified as Timer 0 and Timer 1, and can be independently configured to operate in a variety of modes as a timer or as an event counter. When operating as a timer, the timer/counter runs for a programmed length of time, then issues an interrupt request. When operating as a counter, the timer/counter counts negative

transitions on an external pin. After a preset number of counts, the counter issues an interrupt request.

The various operating modes of each timer/counter are described in the following sections.

2.9.1 Timer/Counter Operations

A basic operation consists of timer registers THx and TLx (x= 0, 1) connected in cascade to form a 16-bit timer. Setting the run control bit (TRx) in TCON register (see Figure 2-3) turns the timer on by allowing the selected input to increment TLx. When TLx overflows it increments THx; when THx overflows it sets the timer overflow flag (TFx) in TCON register. Setting the TRx does not clear the THx and TLx timer registers.

Timer registers can be accessed to obtain the current count or to enter preset values. They can be read at any time but TRx bit must be cleared to preset their values, otherwise the behavior of the timer/counter is unpredictable. The C/Tx# control bit (in TCON register) selects timer operation, or counter operation,

by selecting the divided-down peripheral clock or external pin Tx as the source for the counted signal. TRx bit must be cleared when changing the mode of operation, otherwise the behavior of the timer/counter is unpredictable.

For timer operation (C/Tx# = 0), the timer register counts the divided-down peripheral clock. The timer register is incremented once every peripheral cycle (6 peripheral clock periods). The timer clock rate is FPER / 6, i.e. FOSC / 12 in standard mode or FOSC / 6 in X2 mode.

For counter operation (C/Tx# = 1), the timer register counts the negative transitions on the Tx external input pin. The external input is sampled every peripheral cycle. When the sample is high in one cycle and low in the next one, the counter is incremented. Since it takes 2 cycles (12 peripheral clock periods) to recognize a negative transition, the maximum count rate is FPER / 12, i.e. FOSC / 24 in standard mode or FOSC / 12 in X2 mode. There are no restrictions on the duty cycle of the external input signal, but to ensure that a given level is sampled at least once before it changes, it should be held for at least one full peripheral cycle.

In addition to the “timer” or “counter” selection, Timer 0 and Timer 1 have four operating modes from which to select which are selected by bit-pairs (M1, M0) in TMOD. Modes 0, 1, and 2 are the same for both timer/counters. Mode 3 is different. The four operating modes are described below.

Timer 2, has three modes of operation: ‘capture’, ‘auto-reload’ and ‘baud rate generator’.

Timer 0:

Timer 0 functions as either a timer or event counter in four modes of operation. Figure 2-9 to Figure 2-12 show the logical configuration of each mode. Timer 0 is controlled by the four lower bits of the TMOD register (see Table 2-5) and bits 0, 1, 4 and 5 of the TCON register (see Table 2-3). TMOD register selects the method of timer gating (GATE0), timer or counter operation (T/C0#) and mode of operation (M10 and M00). The TCON register provides timer 0 control functions: overflow flag (TF0), run control bit (TR0), interrupt flag (IE0) and interrupt type control bit (IT0). For normal timer operation (GATE0= 0), setting TR0 allows TL0 to be incremented by the selected input. Setting GATE0 and TR0 allows external pin INT0# to control timer operation.

Timer 0 overflow (count rolls over from all 1s to all 0s) sets TF0 flag, generating an interrupt request.

It is important to stop timer/counter before changing mode.

Mode 0 (13-bit Timer):

Mode 0 configures timer 0 as a 13-bit timer which is set up as an 8-bit timer (TH0 register) with a modulo 32 prescaler implemented with the lower five bits of the TL0 register (see Figure 2-9). The upper three bits of TL0 register are indeterminate and should be ignored. Prescaler overflow increments the TH0 register.

As the count rolls over from all 1’s to all 0’s, it sets the timer interrupt flag TF0. The counted input is enabled to the Timer when TR0 = 1 and either GATE = 0 or INT0 = 1. (Setting GATE = 1 allows the Timer to be controlled by external input INT0, to facilitate pulse width measurements). TR0 is a control bit in the Special Function register TCON (Table 2-3). GATE is in TMOD.

The 13-bit register consists of all 8 bits of TH0 and the lower 5 bits of TL0. The upper 3 bits of TL0 are indeterminate and should be ignored. Setting the run flag (TR0) does not clear the registers.

Mode 0 operation is the same for Timer 0 as for Timer 1. Substitute TR0, TF0 and INT0 for the corresponding Timer 1 signals in Table 2-10. There are two different GATE bits, one for Timer 1 (TMOD.7) and one for Timer 0 (TMOD.3).

Mode 1 (16-bit Timer):

Mode 1 is the same as Mode 0, except that the Timer register is being run with all 16 bits.

Mode 1 configures timer 0 as a 16-bit timer with the TH0 and TL0 registers connected in cascade (see Figure 2-10). The selected input increments the TL0 register.

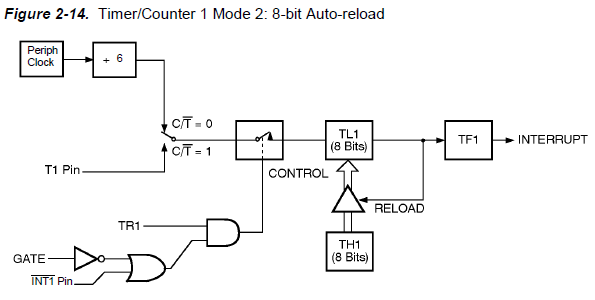

Mode 2 (8-bit Timer with Auto-Reload):

Mode 2 configures timer 0 as an 8-bit timer (TL0 register) that automatically reloads from the TH0 register (see Table 2-5 on page 87). TL0 overflow sets TF0 flag in the TCON register and reloads TL0 with the contents of TH0, which is preset by software. When the interrupt request is serviced, hardware clears TF0. The reload leaves TH0 unchanged. The next reload value may be changed at any time by writing it to the TH0 register.

Mode 2 operation is the same for Timer/Counter 1.

Mode 3 (Two 8-bit Timers):

Mode 3 configures timer 0 so that registers TL0 and TH0 operate as separate 8-bit timers (see Figure 2-12). This mode is provided for applications requiring an additional 8-bit timer or counter. TL0 uses the timer 0 control bits C/T0# and GATE0 in the TMOD register, and TR0 and TF0 in the TCON register in the normal manner. TH0 is locked into a timer function (counting FPER /6) and takes over use of the timer 1 interrupt (TF1) and run control (TR1) bits. Thus, operation of timer 1 is restricted when timer 0 is in mode 3.

Timer 1:

Timer 1 is identical to timer 0, except for mode 3, which is a hold-count mode. The following comments help to understand the differences:

• Timer 1 functions as either a timer or event counter in three modes of operation. Figure 2-9 to Figure 2-11 show the logical configuration for modes 0, 1, and 2. Timer 1’s mode 3 is a hold-count mode.

• Timer 1 is controlled by the four high-order bits of the TMOD register and bits 2, 3, 6 and 7 of the TCON register.

• The TMOD register selects the method of timer gating (GATE1), timer or counter operation (C/T1#) and mode of operation (M11 and M01). The TCON register provides timer 1 control functions: overflow flag (TF1), run control bit (TR1), interrupt flag (IE1) and interrupt type control bit (IT1).

• Timer 1 can serve as the baud rate generator for the serial port. Mode 2 is best suited for this purpose.

• For normal timer operation (GATE1 = 0), setting TR1 allows TL1 to be incremented by the selected input. Setting GATE1 and TR1 allows external pin INT1# to control timer operation.

• Timer 1 overflow (count rolls over from all 1s to all 0s) sets the TF1 flag generating an interrupt request.

• When timer 0 is in mode 3, it uses timer 1’s overflow flag (TF1) and run control bit (TR1). For this situation, use timer 1 only for applications that do not require an interrupt (such as a baud rate generator for the serial port) and switch timer 1 in and out of mode 3 to turn it off and on.

• It is important to stop timer/counter before changing modes.

Mode 0 (13-bit Timer):

Mode 0 configures Timer 1 as a 13-bit timer, which is set up as an 8-bit timer (TH1 register) with a modulo-32 prescaler implemented with the lower 5 bits of the TL1 register (see Figure 2-9). The upper 3 bits of the TL1 register are ignored. Prescaler overflow increments the TH1 register.

Mode 1 (16-bitTimer):

Mode 1 configures Timer 1 as a 16-bit timer with the TH1 and TL1 registers connected in cascade (see Figure 2-10). The selected input increments the TL1 register.

Mode 2 (8-bit Timer with Auto Reload):

Mode 2 configures Timer 1 as an 8-bit timer (TL1 register) with automatic reload from the TH1 register on overflow (see Figure 2-11). TL1 overflow sets the TF1 flag in the TCON register and reloads TL1 with the contents of TH1, which is preset by software. The reload leaves TH1 unchanged.

Mode 3 (Halt):

Placing Timer 1 in mode 3 causes it to halt and hold its count. This can be used to halt Timer 1 when TR1 run control bit is not available i.e., when Timer 0 is in mode 3.

Interrupt:

Each timer handles one interrupt source; that is the timer overflow flag TF0 or TF1. This flag is set every time an overflow occurs. Flags are cleared when vectoring to the timer interrupt routine. Interrupts are enabled by setting ETx bit in IE0 register. This assumes interrupts are globally enabled by setting EA bit in the IE0 register.

Timer Registers:

TCON:

TMOD:

Example 1:

Calculation of Timer 0 reload value needed to achieve timer delay of 20 ms. Oscillator frequency is 11.0592 MHz.

Delay Value = Timer Delay / Timer Clock Cycle Duration

= 36864 (must be rounded to the nearest integer)

Timer Reload Value = Maximum Register Count - Delay Value

= 65535 – 36864

= 28671

= 0x6FFF

so Timer 0 is loaded with:

TH0 = 0x6F;

TL0 = 0xFF;

Example 2:

Function to generate 100 μs delay using timer 0.

Procedure is:

Initialise TMOD register

Initialise TL0 and TH0

Start the Timer

Monitor TF0 until it is set

Delay: MOV TMOD,#01H ; initialise TMOD

MOV TL0,#47H ; initialise TL0

MOV TL0,#FFH ; initialise TH0

SETB TR0 ; start timer

Wait: JNB TF0,Wait ; wait for TF0

CLR TR0 ; stop timer

CLR TF0 ; clear TF0

RET

Timer Reload Value = 65535 – 184 = 65351 = 0xFF47

so Timer 0 is loaded with:

TH0 = 0x6F;

TL0 = 0xFF;

Example 3:

Function to generate 100 μs delay using timer 0. C version of the function from Example 2.

void Delay(void)

{

TMOD = 0x01;

TL0 = 0x47;

TH0 = 0xFF;

TR0 = 1;

while(!TF0)

TR0 = 0;

TF0 = 0;

}

Example 4:

Program to toggle pin 7 on Port 1 with a time delay of 20 ms.

#include <reg51.h>

#define off 0

#define on 1

sbit pin7 = P1^7; // label pin7 is port 1 pin 7

main()

{

TMOD = 0x01; // timer 0 mode 1,

// TH0TL0 = 16 bit register

while(1) // keep repeating the following section

{

pin7 = on; // pin 7 to 5 volts, i.e. logic 1

// use timer 0 to generate delay

TH0 = 0x6F; // hex 6F into TH0

TL0 = 0xFF; // hex FF into TL0

TR0 = on; // start timer

while(!TF0); // wait here until TF0 = 1

TR0 = off; // stop timer

TF0 = off; // clear overflow flag

pin7 = off;// pin 7 to 0 v0lts, i.e. logic 0

// repeat timer delay

TH0 = 0x6F; // hex 6F into TH0

TL0 = 0xFF; // hex FF into TL0

TR0 = on; // start timer

while(!TF0); // wait here until TF0 = 1

TR0 = off; // stop timer

TF0 = off; // clear overflow flag

}

}

Example 5:

Load the timer 0 in order to produce 1 kHz square wave (i.e. cycle time of 1000 μs and delay time 500 μs). Oscillator frequency is 11.0592 MHz.

Timer Reload Value = 65535 – 922 = 64614 = 0xFC66

so Timer 0 is loaded with: TH0 = 0xFC; TL0 = 0x66

Alternatively if we use: TH0 = ~(922/255);

result of integer division 922/255 = 3 will be byte complemented to 0xFC and stored in TH0

Second line to fill up lower timer 0 register: TL0 = -(922%255)

will negate reminder of division 922/255 and store the result in TL0

i.e. 922%255 = 154

-(922%255) = 256-154 = 102 = 0x66

Example 6:

C program to generate 1 kHz square wave from figure below. Square wave should be generated on pin 7 of port 1. Functions are used to generate two delays needed in the program. (delay = 200 μs)

Example 1:

Calculation of Timer 0 reload value needed to achieve timer delay of 20 ms. Oscillator frequency is 11.0592 MHz.

Delay Value = Timer Delay / Timer Clock Cycle Duration

= 36864 (must be rounded to the nearest integer)

Timer Reload Value = Maximum Register Count - Delay Value

= 65535 – 36864

= 28671

= 0x6FFF

so Timer 0 is loaded with:

TH0 = 0x6F;

TL0 = 0xFF;

Example 2:

Function to generate 100 μs delay using timer 0.

Procedure is:

Initialise TMOD register

Initialise TL0 and TH0

Start the Timer

Monitor TF0 until it is set

Delay: MOV TMOD,#01H ; initialise TMOD

MOV TL0,#47H ; initialise TL0

MOV TL0,#FFH ; initialise TH0

SETB TR0 ; start timer

Wait: JNB TF0,Wait ; wait for TF0

CLR TR0 ; stop timer

CLR TF0 ; clear TF0

RET

Timer Reload Value = 65535 – 184 = 65351 = 0xFF47

so Timer 0 is loaded with:

TH0 = 0x6F;

TL0 = 0xFF;

Example 3:

Function to generate 100 μs delay using timer 0. C version of the function from Example 2.

void Delay(void)

{

TMOD = 0x01;

TL0 = 0x47;

TH0 = 0xFF;

TR0 = 1;

while(!TF0)

TR0 = 0;

TF0 = 0;

}

Example 4:

Program to toggle pin 7 on Port 1 with a time delay of 20 ms.

#include <reg51.h>

#define off 0

#define on 1

sbit pin7 = P1^7; // label pin7 is port 1 pin 7

main()

{

TMOD = 0x01; // timer 0 mode 1,

// TH0TL0 = 16 bit register

while(1) // keep repeating the following section

{

pin7 = on; // pin 7 to 5 volts, i.e. logic 1

// use timer 0 to generate delay

TH0 = 0x6F; // hex 6F into TH0

TL0 = 0xFF; // hex FF into TL0

TR0 = on; // start timer

while(!TF0); // wait here until TF0 = 1

TR0 = off; // stop timer

TF0 = off; // clear overflow flag

pin7 = off;// pin 7 to 0 v0lts, i.e. logic 0

// repeat timer delay

TH0 = 0x6F; // hex 6F into TH0

TL0 = 0xFF; // hex FF into TL0

TR0 = on; // start timer

while(!TF0); // wait here until TF0 = 1

TR0 = off; // stop timer

TF0 = off; // clear overflow flag

}

}

Example 5:

Load the timer 0 in order to produce 1 kHz square wave (i.e. cycle time of 1000 μs and delay time 500 μs). Oscillator frequency is 11.0592 MHz.

Timer Reload Value = 65535 – 922 = 64614 = 0xFC66

so Timer 0 is loaded with: TH0 = 0xFC; TL0 = 0x66

Alternatively if we use: TH0 = ~(922/255);

result of integer division 922/255 = 3 will be byte complemented to 0xFC and stored in TH0

Second line to fill up lower timer 0 register: TL0 = -(922%255)

will negate reminder of division 922/255 and store the result in TL0

i.e. 922%255 = 154

-(922%255) = 256-154 = 102 = 0x66

Example 6:

C program to generate 1 kHz square wave from figure below. Square wave should be generated on pin 7 of port 1. Functions are used to generate two delays needed in the program. (delay = 200 μs)

// header file containing SFR adresses

#include<reg51.h>

// to make program more readable:

// define ON and OFF states

#define on 1

#define off 0

// give a name to output pin

sbit pwm = P1^7;

// long and short delay functions

void delay_on();

void delay_off();

main()

{

TMOD = 0x01; // initialise TMOD for Timer 0 in mode 1

while(1) // repeat this

{

pwm = on; // output pin high

delay_on(); // 800 us delay

pwm = off; // output pin low

delay_off(); // 200 us delay

}

}

// 800 us delay function

void delay_on()

{

// loading Timer 0 for longer delay

TH0 = ~(1475/256);

TL0 = -(1475%256);

TR0 = on; // turn the Timer 0 ON

while(!TF0); // wait for timer overflow

TR0 = off; // switch the Timer 0 off

TF0 = off; // clear the overflow flag

}

// 200 us delay function

void delay_off()

{

// loading Timer 0 for shorter delay

TH0 = ~(369/256);

TL0 = -(369%256);

TR0 = on;

while(!TF0);

TR0 = off;

TF0 = off;

}

No comments:

Post a Comment